加速されたAIおよびMLのワークロードは、人工知能(AI)および機械学習(ML)のタスクのパフォーマンスを向上させるために、GPU(グラフィックス処理装置)やTPU(テンソル処理装置)などの特殊なハードウェアアクセラレータを使用することを指します。

課題と要件

加速されたAIおよびMLのワークロードは、処理される大量のデータに対応するために、高帯域幅メモリが必要となることが多いです。現代のアクセラレータの計算能力に見合う高い帯域幅を提供できるメモリアーキテクチャが必要です。これには、より広いメモリバスや高速メモリインターフェイス、あるいは高帯域幅メモリ(HBM)技術の統合など、DRAM設計における革新が含まれる可能性があります。

AIは、大量のデータを生成および処理するデータ集約型アプリケーションです。SMART ModularのNVDIMMは、SafeStor™暗号化を備えた永続メモリであり、ログ記録、ティアリング、キャッシング、書き込みバッファリングのためにシステムパフォーマンスを劇的に加速させ、AIアプリケーションに理想的なメモリソリューションを提供します。NVDIMMは、AIおよびMLアプリケーションのシステムパフォーマンスを劇的に向上させる理想的なソリューションです。

SMARTのDRAMソリューション

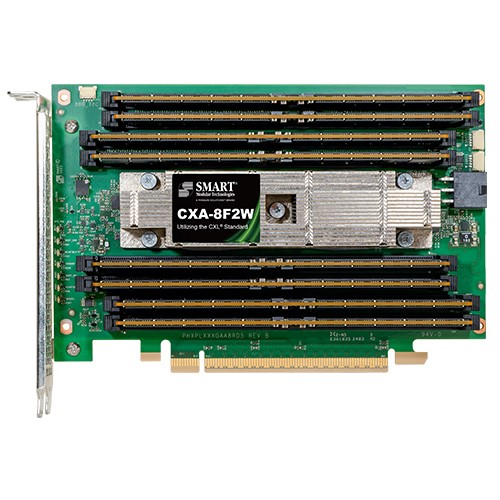

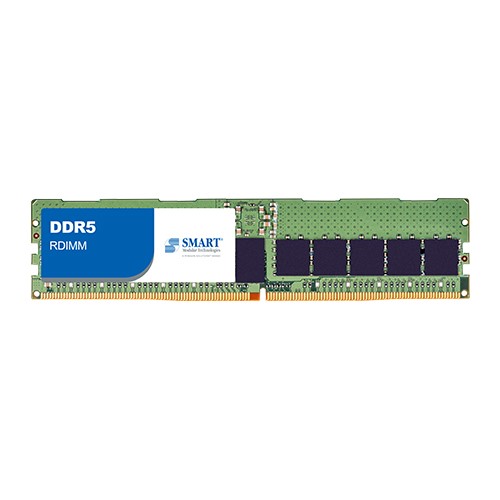

- CXL 8-DIMM AIC - SMARTのCXA-8F2Wは、CXL標準を利用する8-DIMM AICです。これは、8つのDDR5 RDIMMを搭載したType 3 PCIe Gen5 Add-In Card (AIC)で、フルハイト・ハーフレングスのPCIeフォームファクターにマウントされています。2つのx16 CXLコントローラを使用して、2つのx8 CXLポートを実装し、合計64GB/sの帯域幅を提供します。

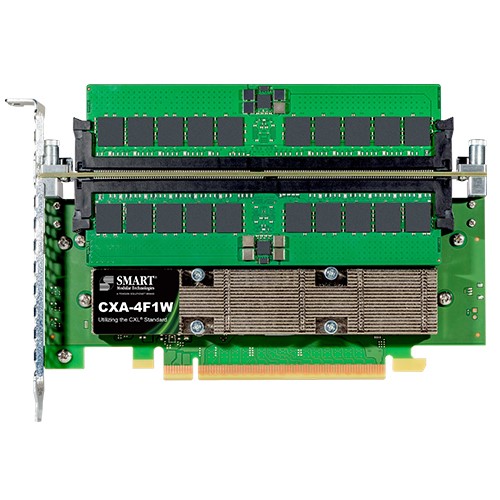

- CXL 4-DIMM AIC - SMARTのCXA-4F1Wは、CXL標準を利用する4-DIMM AICで、Type 3 PCIe Gen5 Add-In Card (AIC)です。4つのDDR5 RDIMMを搭載し、フルハイト・ハーフレングスのPCIeフォームファクターにマウントされています。1つのx16 CXLコントローラを使用して、1つのx16 CXLポートを実装し、合計64GB/sの帯域幅を提供します。

- DDR5 Zefr ZDIMM - ZDIMMs(Zefrメモリーモジュール)は、SMARTのZefr™独自のスクリーニングプロセスを利用しており、業界トップクラスの稼働時間と信頼性を保証しています。ZDIMMsは厳密なテストを受けており、メモリ信頼性の障害の90%以上を排除し、最大のアプリケーション稼働時間を確保し、メモリサブシステムの信頼性を最適化しています。

SMARTのフラッシュソリューション

- DC5820データセンターSSD - SMARTのDC5820 PCIe Gen5 NVMeデータセンターSSDは、ハイパースケール、ハイパーコンバージド、エンタープライズ、エッジデータセンターにおけるストレージシステムへの増大する需要に対応するために設計されています。DC5820データセンターSSDファミリーは、混在するアプリケーションワークロードにおいて業界をリードするKIOPs/Watt性能と優れたQuality of Service (QoS)を提供します。